Thể loại: Bài viết nổi bật » Điện tử thực hành

Số lượt xem: 12919

Bình luận về bài viết: 0

Chip 4046 (K564GG1) cho các thiết bị có khả năng duy trì cộng hưởng - nguyên tắc hoạt động

Khi tạo ra một thiết bị điện tử công suất có khả năng duy trì cộng hưởng trong mạch LC, mạch điều khiển cộng hưởng được thiết kế để đồng bộ hóa các dao động nhận được với các xung điều khiển đến từ trình điều khiển.

Nhiệm vụ của bộ điều khiển này là giữ cho các dao động cộng hưởng trong mạch LC bằng cách kích thích nó kịp thời với các dao động của chính nó. Để đạt được điều này, bộ điều khiển cần nhận tín hiệu từ vòng lặp từ mạch chứa dữ liệu về tần số hiện tại và pha của dao động tự do trong đó, sau đó, dựa vào các dữ liệu này, duy trì giai đoạn trình điều khiển đồng bộ với các tần số và pha này, sau đó cộng hưởng trong mạch sẽ được lưu tự động.

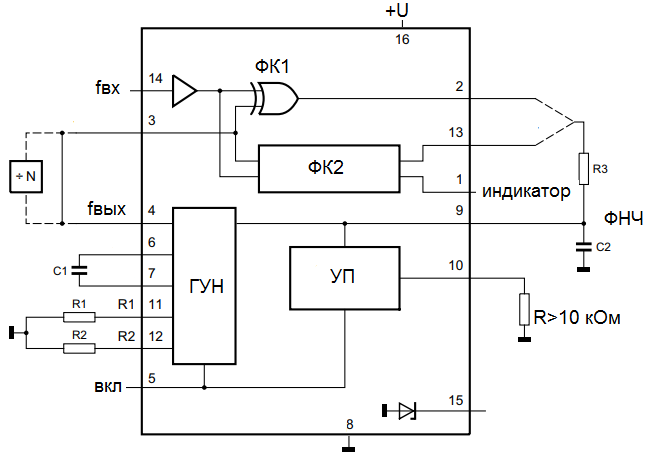

Để xây dựng bộ điều khiển như vậy, chip CD4046 hoặc đối tác trong nước K564GG1 là phù hợp. Chúng ta hãy xem thiết bị của vi mạch này, mục đích kết luận của nó và sơ đồ kết nối của các bộ phận được gắn, để hiểu những gì bạn đang xử lý nếu cần thiết.

Con chip này cho phép bạn dễ dàng tổ chức một vòng lặp khóa PLL. Để xây dựng PLL, ba khối cần thiết được sử dụng được đặt bên trong vi mạch: bộ tạo dao động điều khiển điện áp VCO, bộ so sánh pha FC và bộ lọc thông thấp LPF.

Được tích hợp vào vi mạch, VCO tạo ra một chuỗi các xung hình chữ nhật với độ bao phủ 50%, nghĩa là một máy uốn tinh khiết có tần số ban đầu phụ thuộc vào các tham số của hai mạch RC: R1C1 và R2C2 được kết nối với nó bên ngoài vi mạch và biên độ trong trường hợp này gần với điện áp của vi mạch. U +.

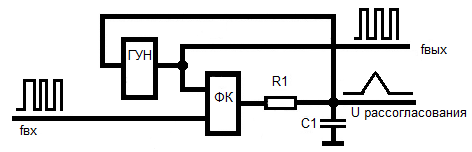

Nguyên tắc hoạt động của PLL

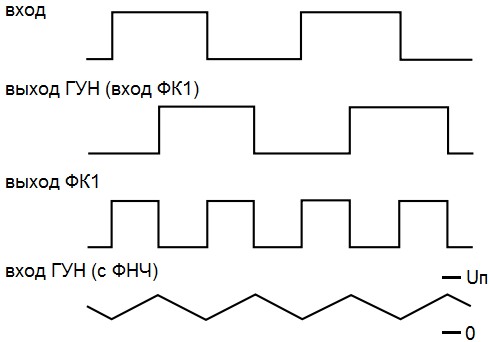

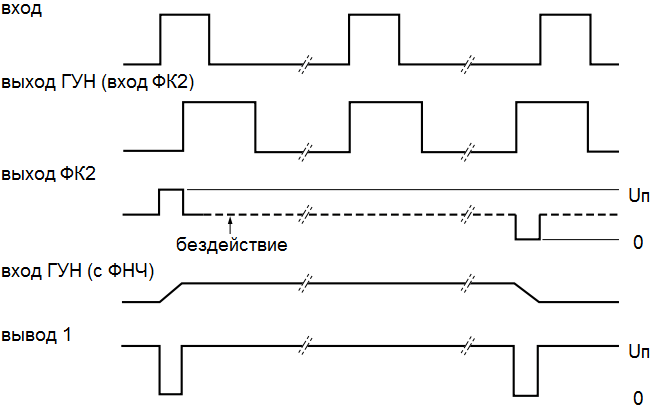

Vây tín hiệu đầu vào bên ngoài được cung cấp cho vi mạch, trên thực tế, cho một trong các đầu vào của bộ so sánh pha FC (FC1 hoặc FC2 - nhà phát triển chọn) bên trong nó. Một uốn khúc được sản xuất bởi VCO đồng thời được đưa vào đầu vào FC thứ hai. Kết quả là, tín hiệu hình chữ nhật thu được ở đầu ra FC, thời lượng xung phụ thuộc vào độ chênh lệch giữa các xung từ VCO và xung ngoài tại mỗi thời điểm.

Trong thực tế, thời lượng của các xung đầu ra với FC tỷ lệ thuận với độ lệch pha của hai tín hiệu được so sánh. Thực tế là phần tử logic OR-thường được sử dụng làm FC, điều này có nghĩa là ở đầu ra FC sẽ chỉ có mức điện áp cao nếu có sự khác biệt giữa các tín hiệu và nếu không có sự khác biệt thì đầu ra từ FC sẽ thấp cấp điện áp hoặc trạng thái không hoạt động.

Từ đầu ra của FC, tín hiệu được đưa đến bộ lọc thông thấp, là mạch RC đơn giản, trên tụ điện có điện áp không phù hợp xung, mức gợn tỷ lệ với chênh lệch của hai tín hiệu (từ VCO bên trong và được cung cấp cho vi mạch từ bên ngoài). .

Điện áp không phù hợp thu được ở tụ LPF ngay lập tức được đưa trở lại đầu vào VCO và tùy thuộc vào giá trị trung bình của nó, tần số VCO sẽ được điều chỉnh tự động để tần số của phần uốn khúc ở đầu ra của nó đạt đến tần số của tín hiệu bên ngoài đến từ bên ngoài của vi mạch. Khi đạt đến tình huống này, điện áp trung bình trên tụ của bộ lọc thông thấp sẽ nhỏ nhất - đây là dấu hiệu của sự khởi đầu của sự hội tụ tối đa của hai tín hiệu theo tần số và pha. Khi tín hiệu được thu như vậy, nó sẽ tiếp tục được giữ bởi vòng lặp PLL.

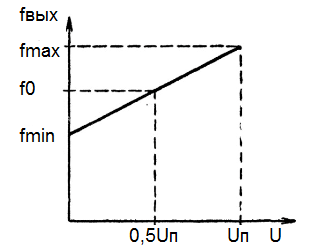

Các giới hạn của việc tổ chức lại VCO

Như bạn đã hiểu, tần số VCO có khả năng điều chỉnh trong một phạm vi tự động điều chỉnh nhất định. Phạm vi này được thiết lập bởi các thành phần bên ngoài của chip. Và tốc độ phản ứng của hệ thống PLL được xác định bởi hằng số thời gian của LFF (giá trị C2 và R3).Vì lý do này, bạn nên nghiêm túc tiếp cận việc lựa chọn các thành phần được gắn của chip.

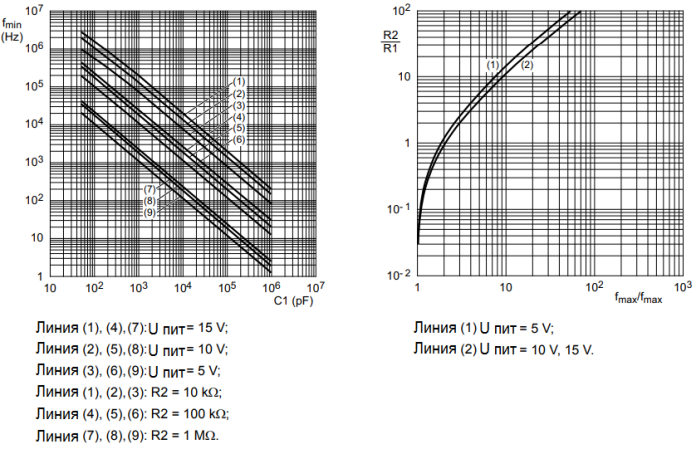

Điện áp cung cấp của vi mạch, tụ điện C1, cũng như các điện trở R1 và R2 xác định dải tần số tự điều chỉnh tần số VCO bên trong vi mạch. Điện trở R2 sai lệch tần số tối thiểu fmin của VCO trên 0. Và tỷ lệ giữa các giá trị của điện trở R1 và R2 xác định tỷ lệ giữa tần số tối đa và tối thiểu - fmax / fmin, tín hiệu đầu ra có thể điều chỉnh từ VCO.

Đầu vào và đầu ra chip

Kết luận 4 - đầu ra tín hiệu của VCO, trên nó ở chế độ làm việc uốn khúc. Đầu ra này có thể được sử dụng để cung cấp tín hiệu cho các khối khác của thiết bị được thiết kế.

Chân 5 chịu trách nhiệm bật và tắt VCO. Khi một điện áp mức cao được áp dụng cho đầu ra này, microcircuit sẽ tắt. Khi áp dụng mức điện áp thấp (khi kết nối chân 5 với dây chung) - vi mạch sẽ hoạt động ở chế độ bình thường.

Kết luận 6 và 7. Tụ điện C1 được kết nối với chúng - đây là tụ điện cài đặt tần số của VCO.

Kết luận 8 - dây nguồn chung của chip.

Điện trở R1 nằm giữa cực 11 và dây chung. Điện trở R2 - giữa cực 12 và dây chung. Đây là những điện trở cài đặt tần số. Điện trở R3 của bộ lọc thông thấp - đến chân 9 và chân 2 hoặc 13 (sự khác biệt giữa chúng sẽ được thảo luận sau), tụ điện C2 của bộ lọc thông thấp nằm giữa chân 9 và dây chung.

Chân 10 là đầu ra của bộ khuếch đại lặp. Điện áp trên nó trong quá trình hoạt động của vi mạch là điện áp không khớp được cung cấp cho bộ lọc thông thấp. Kết luận 10 được thiết kế sao cho điện áp không khớp có thể, nếu cần, có thể dễ dàng cách ly mà không làm tắt tụ điện LPF. Để kết luận này, nó được phép kết nối một điện trở với điện trở hơn 10 kOhm.

Kết luận 15 - trên đó là cực âm của diode zener tích hợp có điện áp ổn định 5,6 volt (điện áp ổn định của diode zener này có thể khác nhau, tùy thuộc vào nhà sản xuất chip). Diode zener này có thể được sử dụng tùy ý trong mạch điện của chip.

Kết luận 16 - cộng với sức mạnh của chip.

Đầu vào và đầu ra của bộ so sánh pha FC1 và FC2

Phần uốn khúc từ đầu ra của VCO được lấy từ đầu 4 và được đưa đến đầu cuối 3, được kết nối qua một bộ khuếch đại với các đầu vào của bộ so sánh pha FC1 và FC2. Nếu muốn, tín hiệu từ VCO có thể được truyền tùy ý qua bộ chia tần số.

Đầu vào 14 là đầu vào tín hiệu và tín hiệu đầu vào được cấp cho nó, cần phải đồng bộ hóa tín hiệu đầu ra ở đầu ra của VCO. Tùy thuộc vào bản chất của tín hiệu đầu vào, nhà phát triển có thể chọn sử dụng bộ so sánh pha nào để sử dụng: FC1 hoặc FC2 và gắn điện trở bộ lọc thông thấp vào bộ so sánh đã chọn (để ghim 2 hoặc 13). Bộ so sánh pha FC2 có chân chỉ thị 1, điện áp mức cao xuất hiện trên nó khi các tín hiệu được đồng bộ hóa tối đa.

Điểm đặc biệt của FC1 là nó là một phần tử logic OR độc quyền đơn giản và chất lượng hoạt động của nó phụ thuộc vào các tham số của bộ lọc thông thấp ở đầu ra của nó. Công việc bắt đầu với tần số trung tâm f0 = (fmax-fmin) / 2, có thể thu được các sóng hài của tần số trung tâm. Nó có khả năng chống ồn cao.

Điểm đặc biệt của FC2 là nó chỉ xử lý các khác biệt dương của các xung được cung cấp cho nó, và do đó chu kỳ nhiệm vụ của các xung do đó không thành vấn đề. Công việc bắt đầu với tần số tối thiểu fmin, không có khả năng bắt được sóng hài của tần số trung tâm. Nó có khả năng chống ồn thấp. Trong bộ lọc thông thấp, cần có tụ điện có dòng rò thấp. FC2 phù hợp hơn để sử dụng trong các mạch điện có cộng hưởng LC.

Lựa chọn các tệp đính kèm

Là bộ lọc thông thấp của bộ lọc thông thấp, điện trở R3 và tụ điện C2 được lắp đặt. Để PLL hoạt động chính xác, hằng số thời gian RC phải lớn hơn hàng chục lần so với tần số bắt PLL gần đúng.

Theo quy định, tần số chụp được nhà phát triển biết gần như, do đó, ban đầu chúng được đặt theo phạm vi tự động điều chỉnh tần số: fmin và fmax. Ký hiệu đầu tiên xác định, có tính đến điện áp cung cấp của vi mạch và fmin cần thiết, các giá trị của R2 và C1.Sau đó, theo biểu đồ thứ hai, dựa trên tỷ lệ yêu cầu fmax / fmin, R1 được chọn. Tốt hơn là cung cấp khả năng điều chỉnh các điện trở trong mạch.

Xem thêm tại electro-vi.tomathouse.com

: