Thể loại: Điện tử thực hành, Thợ điện Novice

Số lượt xem: 74031

Bình luận về bài viết: 0

Chip logic. Phần 9. Trình kích hoạt JK

Một câu chuyện về kích hoạt JK và các thí nghiệm đơn giản để nghiên cứu công việc của mình.

Một câu chuyện về kích hoạt JK và các thí nghiệm đơn giản để nghiên cứu công việc của mình.

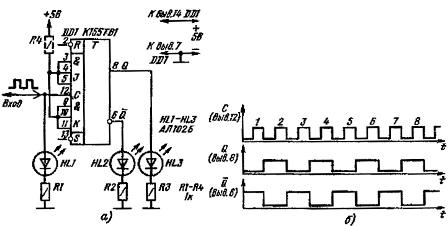

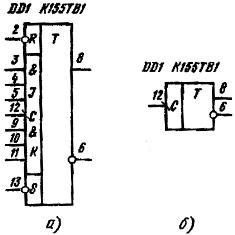

Trong các phần trước của bài viết, các trình kích hoạt như RS và D đã được mô tả. Câu chuyện này sẽ không đầy đủ nếu bạn không đề cập đến Jk kích hoạt. Cũng như Kích hoạt D Nó có logic đầu vào tiên tiến. Trong loạt 155, đây là chip K155TV1 được sản xuất trong gói DIP-14. Sơ đồ chân của nó, hoặc như họ nói bây giờ, sơ đồ chân (từ mã PIN - pin tiếng Anh) được hiển thị trong Hình 1a. Tương tự nước ngoài SN7472N, SN7472J.

Nếu bất kỳ kết luận nào không được sử dụng trong một mạch cụ thể, thì việc hiển thị nó là hoàn toàn chấp nhận được, như trong Hình 1b.

Mô tả và mục đích của kết luận

Bộ kích hoạt K155TV1 có đầu ra trực tiếp và nghịch đảo. Trong hình, đây là kết luận lần lượt 8 và 6. Mục đích của chúng giống như các kích hoạt được xem xét trước đây của loại D và RS. Lối ra ngược bắt đầu trong một vòng tròn nhỏ.

Trên đầu vào R và S, kích hoạt hoạt động giống như một đơn giản Kích hoạt RS. Mức làm việc cho các đầu vào này thấp, được biểu thị bằng các vòng tròn ở gốc của các thiết bị đầu cuối. Cũng như trình kích hoạt D, các đầu vào này được ưu tiên: sự xuất hiện và giữ mức thấp ở một trong số chúng cấm các đầu vào còn lại và một xung âm ngắn sẽ chuyển kích hoạt sang trạng thái tương ứng cho đến khi xung tiếp theo ở đầu vào C.

Đầu vào C được đặt xung nhịp. Khi kích hoạt hoạt động ở chế độ đếm, nó đóng vai trò của thông tin - chính xác là nó sẽ xuất hiện xung đếm. Trong chế độ nhận và lưu trữ thông tin, nó hoạt động như một đồng hồ, mục đích của nó tương tự như đầu vào tương tự của trình kích hoạt D, nhưng logic hoạt động có phần khác nhau và được xác định bởi trạng thái của các đầu vào JK.

Hình 1. Sơ đồ chân của chip K155TV1.

J và K là các đầu vào điều khiển kích hoạt. Chúng được kết hợp theo sơ đồ 3I, được biểu thị bằng ký hiệu & logic I. trên biểu tượng đồ họa. Thông thường, các đầu vào này chỉ đơn giản kết nối với nhau trong các mạch, hóa ra nó có một đầu vào J và một K. Một số dòng chip cũng có bộ kích hoạt JK, chúng còn được gọi là TB1, nhưng không giống như dòng 155, chúng có một đầu vào J và K. Logic công việc trên các đầu vào này hoàn toàn giống với K155TV1, nhưng bạn không cần phải thu thập 3 tín hiệu logic cấp cao cùng nhau. Một ví dụ về các vi mạch như vậy có thể phục vụ, ví dụ, K176TV1, K561TV1, K1564TV1.

Học logic của trình kích hoạt JK

Để tìm hiểu thêm về hoạt động của trình kích hoạt JK, bạn chỉ cần bật nó, như trong bài viết trước, trên bảng mạch và gửi thủ công các tín hiệu đầu vào. Thật vậy, bạn phải thừa nhận rằng bạn có thể ghi nhớ một hướng dẫn tự học khi chơi guitar hoặc accordion nút, nhưng không cần chọn nhạc cụ, bạn đã giành được học cách chơi. Ngoài ra trong trường hợp của microcircuits: cho đến khi bạn tiến hành các thí nghiệm đơn giản nhất, sẽ rất khó để hiểu ý nghĩa của công việc.

Là tín hiệu đầu vào, giống như khi nghiên cứu trình kích hoạt D, chúng ta sẽ sử dụng một nút nhảy dây được kết nối với một dây chung.

Mạch để kiểm tra trình kích hoạt JK K155TV1 được hiển thị trong Hình 2.

Hình 2. Kiểm tra trình kích hoạt JK K155TV1.

Điện áp cung cấp được cung cấp như bình thường cho kết luận thứ 14 và thứ 7 của vi mạch, được biểu thị trên sơ đồ dưới dạng dây dẫn có mũi tên.

Để quan sát trực quan trạng thái của bộ kích hoạt với đầu ra của nó, trực tiếp và nghịch đảo, các chỉ báo LED được kết nối. Chỉ báo tương tự được kết nối với đầu vào C. Đèn LED phát sáng cho biết sự hiện diện của mức đơn vị logic (2.4 ... 5V) ở đầu ra này. Ở đầu vào C, mức tín hiệu đầu ra của bộ tạo xung được kết nối với đầu vào C sẽ được hiển thị. Tất nhiên, trạng thái của đầu vào và đầu ra ở tần số thấp như vậy hoàn toàn có thể quan sát được với một vôn kế thông thường, nhưng điều này không thuận tiện lắm.

Hoạt động kích hoạt JK trên RS - đầu vào

Mặc dù mạch điện trở nên rất đơn giản trước khi bật, nhưng thông thường, bạn nên kiểm tra xem nó có bị lỗi, đoản mạch và đứt không: thậm chí chỉ cần bật nguồn theo hướng ngược lại có thể khiến microcircuit không thể sử dụng được. Quy tắc này nên được ghi nhớ và áp dụng trong tất cả các trường hợp như vậy, ngay cả khi nó chỉ là một mạch điện không có thiết bị bán dẫn.

Vì vậy, bật nó lên. Khi bạn bật lần đầu, một trong các đèn LED ở đầu ra phải sáng, không rõ. Điều này là do quá độ khi bật. Bây giờ chúng tôi sẽ áp dụng mức logic thấp, sử dụng bộ nhảy dây đã nói ở trên, xen kẽ với các đầu vào R và S. Trong trường hợp này, đèn LED ở đầu ra nên luân phiên chuyển đổi, cho biết trạng thái của bộ kích hoạt. Chế độ hoạt động này được gọi là không đồng bộ - nó không yêu cầu tín hiệu nhấp nháy (enable, clock) bổ sung.

Không cần thiết phải áp dụng đồng thời mức thấp trực tiếp cho đầu vào R và S: trạng thái này được coi là bị cấm đối với kích hoạt. Mặc dù nó sẽ không dẫn đến hậu quả không thể đảo ngược dưới dạng đầu ra của vi mạch, trạng thái của các đầu ra trong trường hợp này sẽ không xác định, không tương ứng với logic của bộ kích hoạt. Nếu mọi thứ đều ổn, thì bạn có thể đi đến các thí nghiệm nghiên cứu hoạt động của một bộ kích hoạt trên các đầu vào JK.

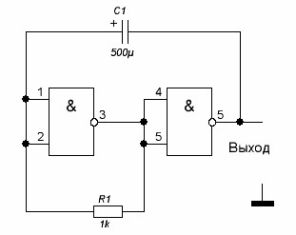

Điều gì xảy ra nếu một dây thấp được áp dụng cho các đầu vào JK bằng dây nhảy? Không có gì cả: kích hoạt sẽ lưu trữ trạng thái trước đó, sẽ được hiển thị bằng ánh sáng của các chỉ báo. Để các đầu vào này ảnh hưởng đến trạng thái kích hoạt, cần phải áp xung cho đầu vào C từ máy phát, mạch được hiển thị trong Hình 3. Để lắp ráp nó, cần có thêm chip K155LA3. Tốc độ và thời gian lặp lại xung phải sao cho có thể theo dõi trực quan trạng thái kích hoạt.

Hình 3. Trình tạo đồng hồ.

Hoạt động kích hoạt JK trong chế độ đếm

Nếu các đầu vào JK được kết nối, như trong Hình 2a, thì bộ kích hoạt sẽ hoạt động ở chế độ đếm: trạng thái của bộ kích hoạt sẽ thay đổi theo từng xung đầu vào. Điện trở R4 được hiển thị trong sơ đồ với một đường chấm chấm - bạn không thể đặt nó, bởi vì các đầu vào không được kết nối vẫn ở trạng thái của một đơn vị logic. Mục đích chính của điện trở này là để bảo vệ chống nhiễu thông qua các đầu vào JK.

Sơ đồ thời gian của trình kích hoạt JK được hiển thị trong Hình 2b và nó rất giống với sơ đồ tương tự cho trình kích hoạt D. Sự khác biệt chính là sự thay đổi trạng thái kích hoạt không xảy ra do chênh lệch mức dương ở đầu vào C, mà là âm - sự chuyển đổi mức xung đầu vào từ mức cao sang mức thấp.

Dễ dàng thấy rằng tần số của các xung ở đầu ra của bộ kích hoạt thấp hơn chính xác hai lần so với tần số của các xung đầu vào. Do đó, kích hoạt trong chế độ đếm thường được sử dụng làm bộ chia tần số cho hai. Hai kích hoạt được bao gồm trong chuỗi sẽ chia tần số thành bốn và ba kích hoạt sẽ được chia thành tám, và cứ thế theo sức mạnh của 2.

Nếu một bộ chia tần số với tỷ lệ phân chia lẻ được yêu cầu, thì một số kích hoạt có phản hồi được sử dụng, nhưng điều này sẽ được thảo luận trong phần tiếp theo của bài viết về bộ đếm và bộ giữ xung.

Từ những điều đã nói ở trên, chúng ta có thể kết luận: nếu các đầu vào JK đồng thời ở trạng thái của một đơn vị logic (mức cao), thì trình kích hoạt hoạt động ở chế độ đếm. Điều này có nghĩa là với mỗi mức chênh lệch mức âm ở đầu vào C, trạng thái kích hoạt sẽ thay đổi ngược lại.

Hoạt động kích hoạt trên đầu vào JK

Điều gì xảy ra nếu một mức 0 logic xuất hiện ở các đầu vào JK? Để kiểm tra điều này, đủ để kết nối ít nhất một đầu vào JK (nhớ lại rằng K155TV1 có 3 đầu vào J và 3 K, kết hợp theo mạch 3I) với một dây chung. Nhưng bạn có thể kết nối với dây chung và tất cả các đầu vào của JK, điều này đã không được cung cấp. Theo các chỉ báo LED, chúng ta thấy rằng các xung đồng hồ đang đến và trạng thái kích hoạt không thay đổi.Ở trạng thái khi logic 0 trên đầu vào J và K, JK - trigger đang ở chế độ lưu trữ thông tin.

Nó vẫn còn để xem xét hai trường hợp. Trường hợp một là khi đầu vào J cao và đầu vào K thấp. Trong tình huống này, kích hoạt ở đầu vào C được đặt thành một trạng thái duy nhất - chỉ báo HL3 được kết nối với đầu ra trực tiếp của kích hoạt sáng lên. HL2, tất nhiên, được hoàn trả.

Nếu trạng thái của các đầu vào JK không thay đổi trong tương lai, thì mỗi xung ở đầu vào C cũng sẽ có xu hướng đặt kích hoạt thành một trạng thái duy nhất, mặc dù nó đã ở trong đó. Trong trường hợp này, họ nói rằng tại đầu vào C, trạng thái kích hoạt trước đó trong trường hợp này được xác nhận đơn giản.

Trường hợp thứ hai là khi đầu vào J bằng 0 và đầu vào K là một. Ở trạng thái này, trên các đầu vào JK, xung đầu tiên ở đầu vào C, bộ kích hoạt đặt thành 0 (được đặt lại) - chỉ báo HL3 tắt và bật HL2. Nếu trạng thái của các đầu vào JK không thay đổi, thì đầu vào C cũng xác nhận trạng thái, như được mô tả ở trên, chỉ lần này là 0.

Vì vậy, để dễ nhớ hơn, hãy tóm tắt: hai đơn vị ở đầu vào của JK là chế độ đếm. Điều này được hiểu rằng điều kiện 3I được đáp ứng cho các đầu vào JK: một trên cả ba đầu vào J và một trên cả ba đầu vào K.

Hai số không trên các đầu vào JK - chế độ lưu trữ thông tin: các xung ở đầu vào C của trạng thái kích hoạt không thể thay đổi. Để có được trạng thái như vậy, đủ ít nhất một đầu vào J Và ít nhất một đầu vào K có mức 0 logic.

Trong trường hợp khi cả ba đầu vào J đều cao, kích hoạt được đặt thành một trạng thái duy nhất. Đồng thời, ít nhất một trong 3 đầu vào của K phải có mức thấp.

Để đặt lại kích hoạt, không phải có mặt trên ít nhất một trong các đầu vào J và một đầu vào phải được giữ trên cả ba đầu vào K.

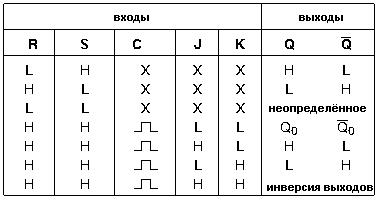

Mọi thứ đã được viết ở trên có thể được tìm thấy trong bảng chân lý cho trình kích hoạt K155TV1, được hiển thị trong Hình 4.

Hình 4. Bảng chân lý cho chip K155TV1.

Các loại kích hoạt khác nhau cũng được sử dụng như các yếu tố của thiết bị đếm, hoặc đơn giản là bộ đếm, cũng như bộ giữ xung. Điều này sẽ được thảo luận trong phần tiếp theo của bài viết về các mạch logic.

Tiếp tục bài viết: Chip logic. Phần 10. Làm thế nào để thoát khỏi sự nảy của danh bạ

Sách điện tử -Hướng dẫn cho người mới bắt đầu với Vi điều khiển AVR

Xem thêm tại electro-vi.tomathouse.com

: